With the decrease of signal rising time and the increase of signal frequency, the EMI problem of electronic products has attracted more and more attention from electronic engineers. Almost 60% of EMI problems can be solved by using high-speed PCB. By and large, here are 9 basic rules:

Rule 1: High-speed signal line routing shielding rules

In high-speed PCB layout, key high-speed signal lines such as clocks and traces need to be shielded. If they are not shielded or only partially shielded, which will cause EMI leakage. It is recommended that the shielded wire be grounded with a hole per 1000mil.

Rule 2: Closed-loop routing rules for high-speed signals

Due to the increasing density of PCB boards, a number of PCB layout engineers are prone to a mistake in the process of routing, that is, high-speed signal networks such as clock signals, which produce closed-loop results when routing multi-layer PCBs. As a result, such a closed loop will produce a loop antenna and increase the EMI radiation intensity.

Rule 3: Open-loop routing rules for high-speed signals

Rule 2 mentions that the closed loop of high-speed signals will cause EMI radiation, but the open loop will also cause EMI radiation.

For high-speed signal networks such as clock signals, once an open-loop result occurs when the multilayer PCB is routed, a linear antenna will be generated, which increases the EMI radiation intensity.

Rule 4: Characteristic impedance continuity rule of high-speed signal

For high-speed signals, it is necessary to ensure the continuity of characteristic impedance when switching between layers, otherwise it will increase EMI radiation. In other words, the width of the wiring of the same layer must be continuous, and the impedance of the wiring of different layers must be continuous.

Rule 5: Wiring direction rules for high-speed PCB design

The wiring between two adjacent layers must follow the principle of vertical wiring, otherwise it will cause crosstalk between the lines and increase EMI radiation.

In short, adjacent wiring layers follow the horizontal and vertical wiring directions, and vertical wiring can suppress crosstalk between lines.

Rule 6: Topological structure rules in high-speed PCB design

In high-speed PCB design, the control of the characteristic impedance of the circuit board and the design of the topology under multiple loads directly determine the success or failure of the product.

The daisy-like chain topology is generally beneficial when used in a few Mhz. It is recommended to use a star-shaped symmetrical structure on the back end in high-speed PCB layout.

Rule 7: Resonance rule of trace length

Check whether the length of the signal line and the frequency of the signal constitute resonance, that is, when the length of the wiring is an integer multiple of the signal wavelength 1/4, the wiring will resonate, and the resonance will radiate electromagnetic waves and cause interference.

Rule 8: Return path rules

All high-speed signals must have a good return path. Try to ensure that the return path of high-speed signals such as clocks is minimized. Otherwise it will greatly increase the radiation, and the size of the radiation is proportional to the area enclosed by the signal path and the return path.

Rule 9: Decoupling capacitor placement rules for devices

The location of the decoupling capacitor is very important. Unreasonable placement will not have the effect of decoupling. The principle is: close to the pins of the power supply, and the area enclosed by the power traces and ground wires of the capacitor is the smallest.

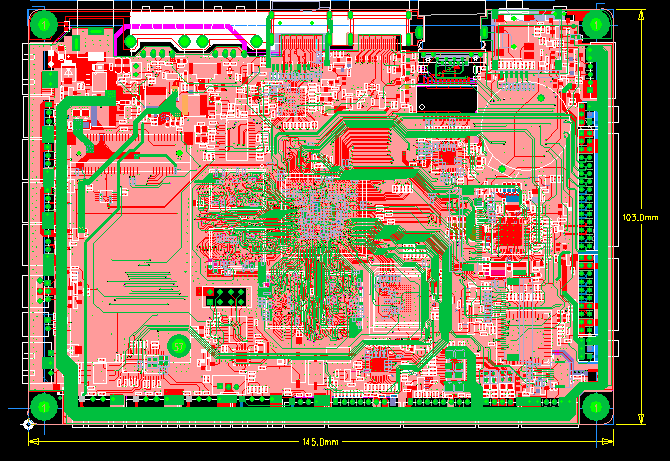

Grande’s PCB Layout Ability

The highest signal layout rate: 10Gbps CML differential signal;

The highest PCB layout layers: 40 layers;

Minimum trace width: 2.4mil;

Minimum trace spacing: 2.4mil;

Minimum BGA PIN spacing: 0.4mm;

Minimum mechanical hole diameter: 6mil;

Minimum laser drilling diameter: 4mil;

Maximum PIN number: 63000+

Maximum number of components: 3600;

Maximum number of BGA: 48+.